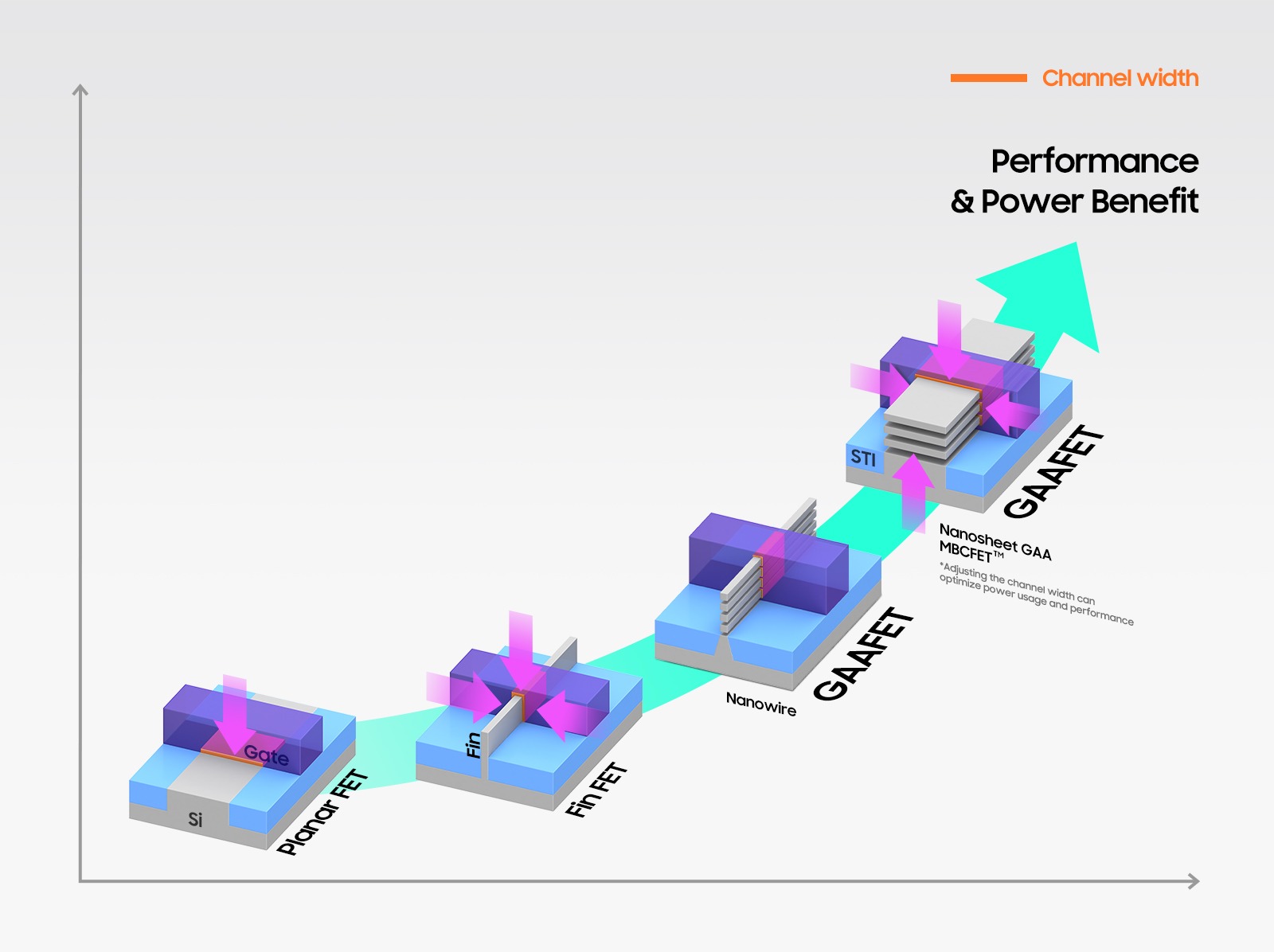

Bahagian semikonduktor Samsung Foundry mengumumkan bahawa ia telah memulakan pengeluaran cip 3nm di kilangnya di Hwasong. Tidak seperti generasi sebelumnya, yang menggunakan teknologi FinFet, gergasi Korea kini menggunakan seni bina transistor GAA (Gate-All-Around), yang meningkatkan kecekapan tenaga dengan ketara.

Cip 3nm dengan seni bina MBCFET (Multi-Bridge-Channel) GAA akan memperoleh kecekapan tenaga yang lebih tinggi, antara lain, dengan mengurangkan voltan bekalan. Samsung juga menggunakan transistor plat nano dalam cip semikonduktor untuk set cip telefon pintar berprestasi tinggi.

Berbanding dengan teknologi wayar nano, plat nano dengan saluran yang lebih luas membolehkan prestasi yang lebih tinggi dan kecekapan yang lebih baik. Dengan melaraskan lebar plat nano, pelanggan Samsung boleh menyesuaikan prestasi dan penggunaan kuasa mengikut keperluan mereka.

Anda mungkin berminat

Berbanding dengan cip 5nm, menurut Samsung, yang baharu mempunyai prestasi 23% lebih tinggi, penggunaan tenaga 45% lebih rendah dan kawasan 16% lebih kecil. Generasi ke-2 mereka kemudiannya akan menawarkan prestasi 30% lebih baik, kecekapan 50% lebih tinggi dan kawasan 35% lebih kecil.

“Samsung berkembang pesat apabila kami terus menunjukkan kepimpinan dalam penerapan teknologi generasi akan datang dalam pembuatan. Kami berhasrat untuk meneruskan kepimpinan ini dengan proses 3nm pertama dengan seni bina MBCFETTM. Kami akan terus berinovasi secara aktif dalam perkembangan teknologi yang kompetitif dan mencipta proses yang membantu mempercepatkan pencapaian kematangan teknologi.” kata Siyoung Choi, ketua perniagaan semikonduktor Samsung.